计算机组成原理

第一章

计算机系统的层次结构

第一层是微程序设计级。这是计算机的最底层——硬件层,它的设计方式:一种是微程序设计方式,另一种是硬布线设计方式。第二层是机器指令系统级,它所提供的是那些计算机硬件可以读懂并可直接操作计算机硬件工作的二进制信息。第三层是操作系统级即虚拟机,它由操作系统负责实现。这是计算机操作系统的操作者和管理员所见到的计算机系统。第四层是语言处理程序及其他系统软件级。语言处理程序的功能是用翻译程序将高级语言编写的源程序翻译成机器语言程序。第五层是面向 用户的应用程序级。它是针对计算机用户在某一应用领域为专门问题而开发的应用软件。

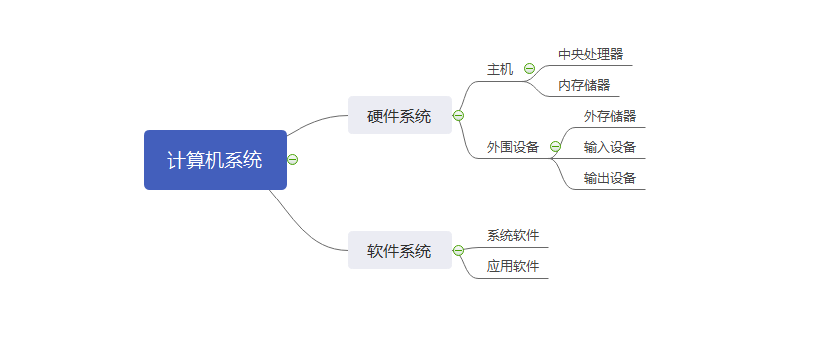

计算机系统由硬件系统和软件系统组成。

计算机的性能指标

机器字长;存储容量;运算速度;可配置的外围设备;性能价格比;可靠性、可维护性和可用性

冯诺依曼体系结构

组成(5部分):运算器、存储器、控制器、输入设备、输出设备

五个特点:1、采用二进制形式表示数据和指令;指令由操作码和地址码组成。2、采用存储程序,即把编写好的程序和原始数据预先放入计算机存储器中,使计算机工作时能够连续、自动、高速地从存储器中取出一条条指令并执行。3、指令的执行时顺序的,即一般按照指令在存储器中存放的顺序执行,程序分支由转移指令实现。4、计算机硬件系统由运算器、控制器、存储器、输入设备和输出设备五大部件组成,并规定五大不见的基本功能。5、计算机以运算器为中心,输入输出设备与存储器之间的数据传送通过运算器完成

- 存储器:计算机用于存放指令和数据的部件

- 运算器:在控制器的控制下,完成加减乘除运算、逻辑运算

- 控制器:计算机的控制部件,也是整个计算机的控制中心,其功能是对当前指令所需要完成的操作进行译码分析,产生各个部件所需要的控制信号,通过向计算机的各个部件发送控制信号,使整个计算机自动、协调地工作

- 输入设备:向计算机输入信息的设备

- 输出设备:将计算机的处理结果转换成人们或其他设备所能接收的形式

第三章(计算题)

数据的表示(补码、反码、译码)

原码

正数符号位为0,负数符号位为1

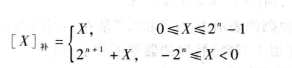

补码

取反码后+1

0:+;1:-

定点整数:结果不带符号位

小数:结果不带符号位

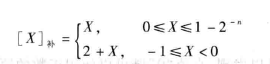

反码

按位取反

定点整数:结果不带符号位

小数:结果不带符号位

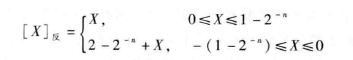

移码

1:+;0:-,数值部分等同于补码

定点整数:

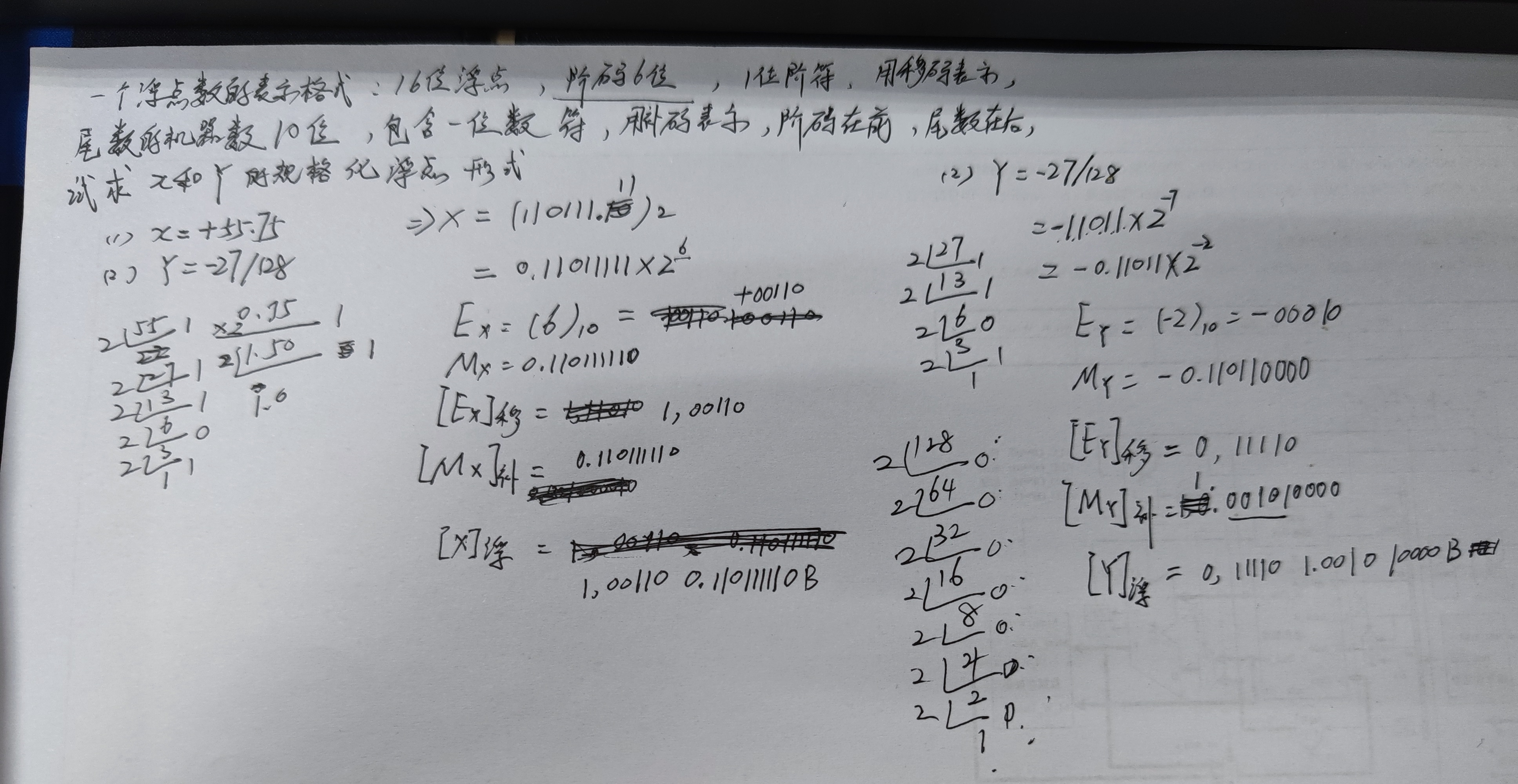

浮点数 P83例题

浮点数由三个决定其数值大小:阶码E、尾数M和阶码的底R

$$

N=M \times R^E

$$

第四章(电路)

加法P104

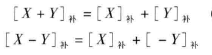

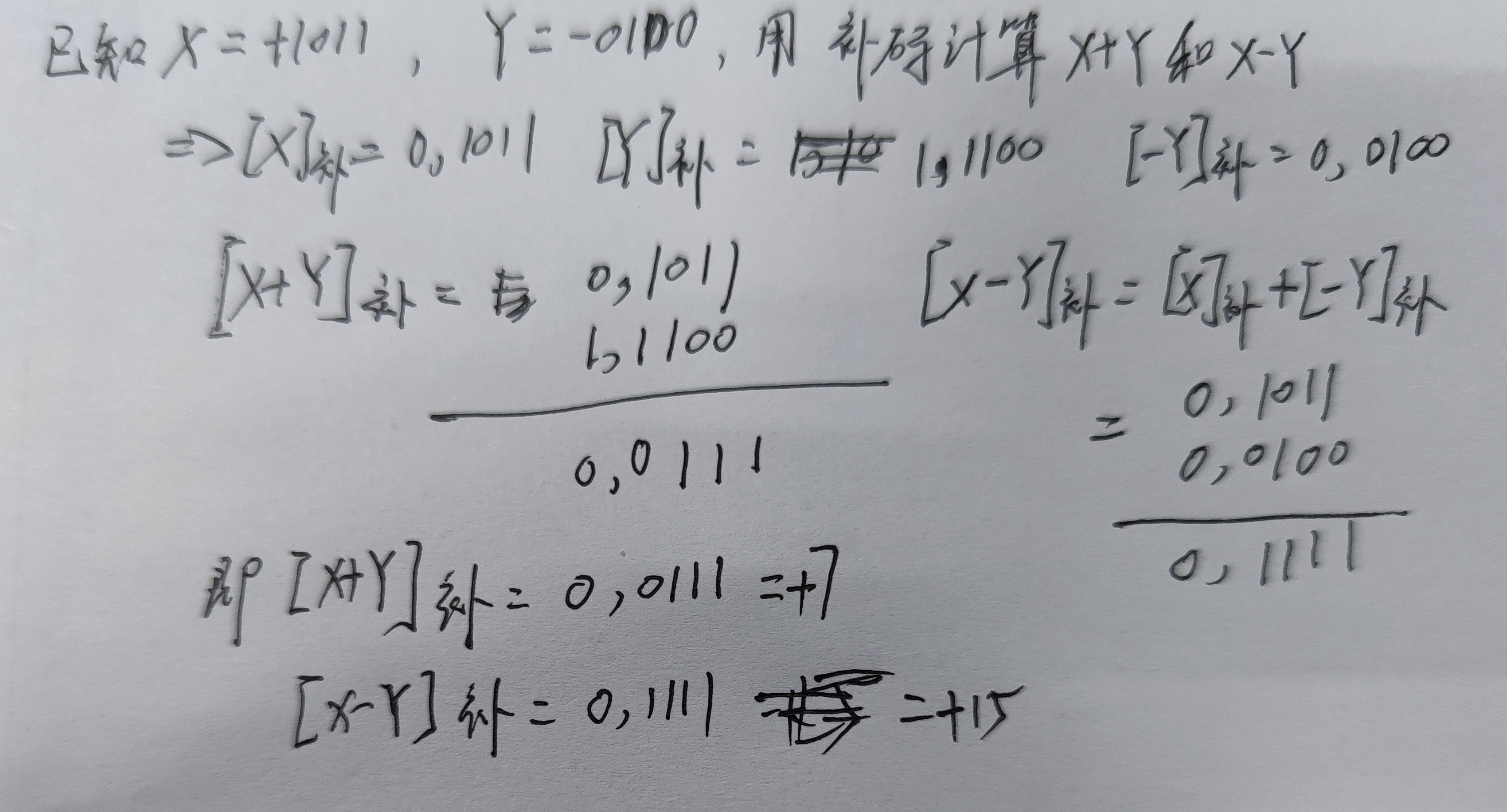

P108 补码的加减运算 画出来 控制信号

溢出情况

| 运算 | 操作数X | 操作数Y | 结果S |

|---|---|---|---|

| X+Y | 正数 | 正数 | 负数 |

| X+Y | 负数 | 负数 | 正数 |

| X-Y | 负数 | 正数 | 正数 |

| X-Y | 正数 | 负数 | 负数 |

$$\overline{\text{ADD}}/SUB$$为加减法控制,0为加法1为减法。A中存放的是被减数/被加数的补码。B中存放的为减数/加数的补码。当$$\overline{\text{ADD}}/SUB$$为1时,B取反,然后+$$\overline{\text{ADD}}/SUB$$达到减数的补码变为-减数的补码,完成减法运算

Ct为符号位,C1为进位位,如果二者异或,v为1是溢出

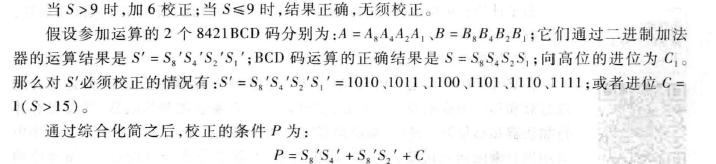

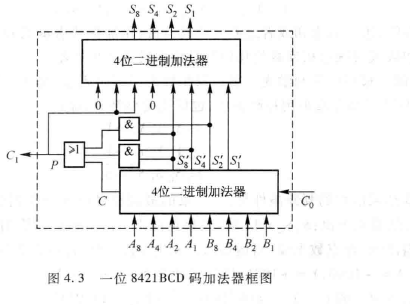

BCD码

BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制)和十进制之间的转换得以快捷的进行。

P112 8421加法器

8421指每个二进制位上所代表的数字的大小分别为8、4、2、1

p=1,+6校正,否则不需要校验

输入的A8、A4、A2、A1;B8、B4、B2、B1,进行运算,得出四位结果S’以及一位进位位C,进行判断S‘的值是否大于9,则进行逻辑判断,得出C1,如果C1=1,则0110=6与S’进行加法运算,进行修正

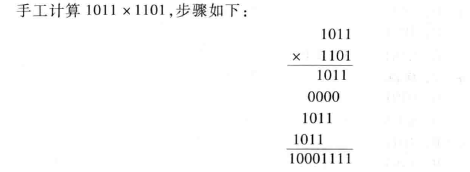

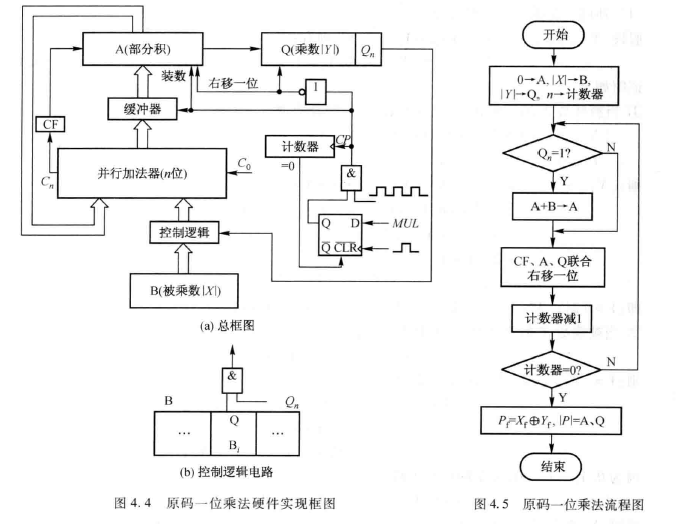

P115 原码乘法

- 手工计算乘法

绝对值乘法的机器算法:从乘数的最低位开始,每次根据乘数位得到其位积,乘数位为0,位积为0,乘数位为1,则位积为被乘数;用原部分积右移一位加上本次位积,得到新部分积;初始部分积为0;循环累加右移n次

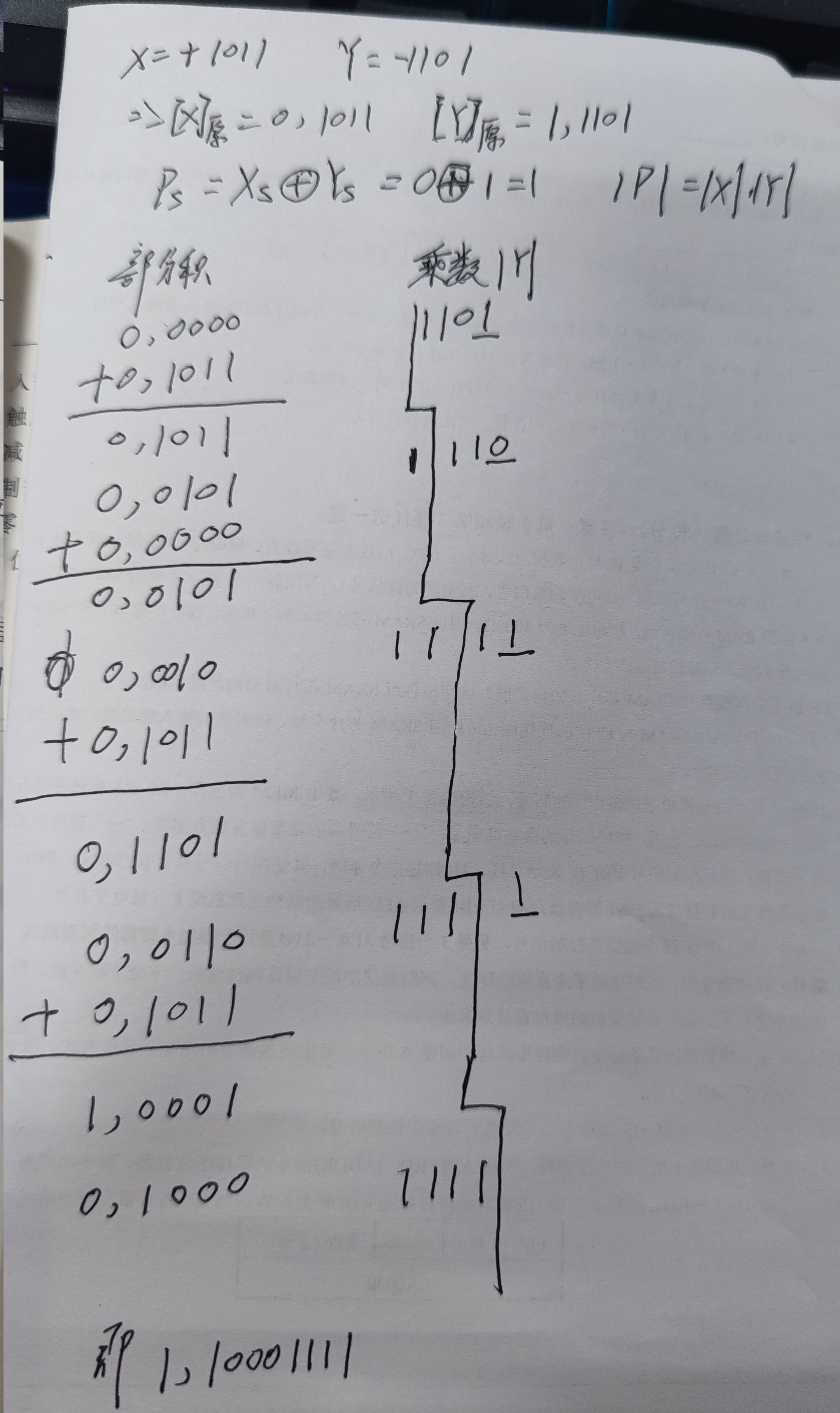

原码一位乘法

符号位单独提出,做异或运算

之后进行绝对值乘法运算

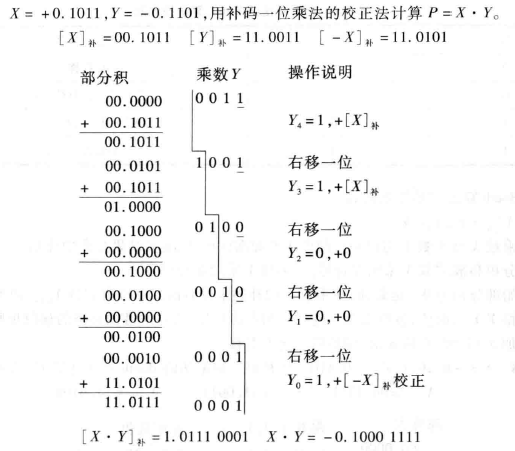

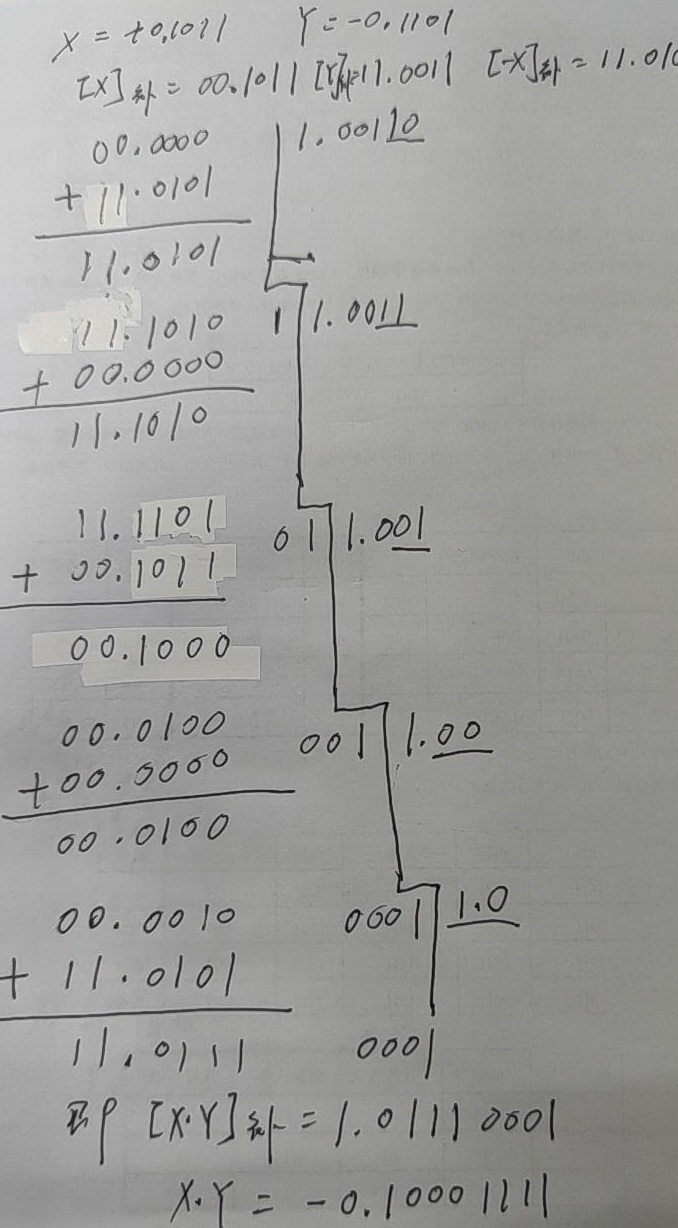

P119 补码乘法 booth算法

补码的乘法

x的补码乘以y的数值部分,加上y的符号位乘以-x的补码,结果积为补码

Booth算法

1、被乘数X和乘数Y均以补码的形式参与乘法运算,运算结果是积的补码

2、部分积和被乘数X采用双符号位,乘数Y采用单符号位

3、初始部分积为0,运算前,在乘数Y的补码末位后添加一位附加位Yn+1,初始值为0.

4、根据YnYn+1的值,查表,累加右移操作。

Yn Yn+1 操作 0 0 +0,右移一位 0 1 +[x]补,右移一位 1 0 +[-x]补,右移一位 1 1 +0,右移一位 5、累加n+1次,右移n次,最后一次算出结果后不右移

第五章(重点)

存储器的层次结构

位于最上层的是寄存器,它的容量很小,访问时间是几个纳秒,可以满足CPU的要求。第二层是高速缓存,他的容量可以是几兆字节,它的的访问时间是寄存器的几倍。第三层是主存,在各种不同类型的存储器里,贮存是最重要的部分,因为计算机当前正在执行的程序和处理的数据都是存放在主存中的,任何程序如果要在计算机中执行,首先必须将其调入主存。主存容量一般在几十到数千兆字节之间,他的访问时间是几十个纳秒。再往下是辅存,它的容量更大,包括硬盘、软盘、光盘等,速度更慢

存储器的性能指标

存储器的性能指标主要有3个:存储容量、速度和价格

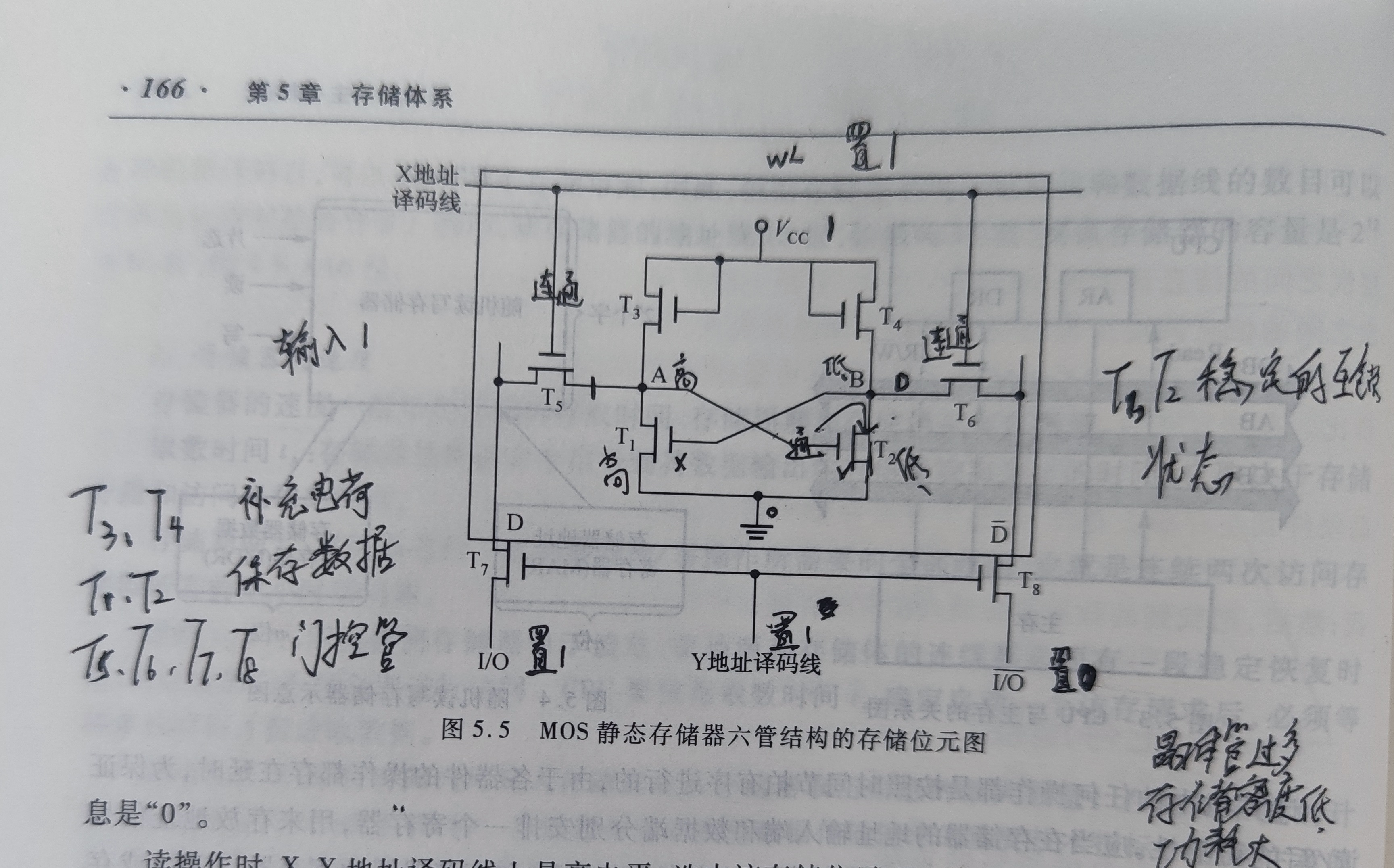

存储单元的实现

| RAM和DRAM的主要异同点: | SRAM | DRAM |

|---|---|---|

| 使用的MOS管 | SRAM使用的MOS管多 | DRAM使用的MOS管少 |

| 功耗与集成度 | 功耗高,集成度低 | 功耗低,集成度高 |

| 是否需要刷新 | 否 | 是 |

| 读写速度 | 快 | 慢 |

Cache(基本原理、程序的局部性原理、地址映射方式、替换算法)

基本原理:

cache是一种小容量高速缓冲存储器,由快速的SRAM组成,直接制作在CPU芯片内,速度几乎与CPU一样快。在CPU和主存之间设置cache,总是把主存中频繁访问的活跃程序和数据块复制到cache中。由于程序访问的局部性,CPU几乎总能从cache中取得指令和数据,而不必访问主存。为便于cache和主存间交换信息,cache和主存空间都被划分为相等的区域。主存中的区域称为块(主存块),它是cache和主存之间信息交换的单位;cache中存放的一个主存块的区域称为行或槽。因此,主存块大小等于cache行中数据区小。程序局部性原理:在较短的时间内,程序产生的地址往往集中在一个很小的范围内,这种现象被称为程序访问的局部性:空间局部性、时间局部性

地址映射方式:

- 直接映射:主存中的一个块只能映射到Cache的某一特定块中去。

- 全相联映射:主存中任何一块都可以映射到Cache中的任何一块位置上。

- 组相联映射:主存和Cache都分组,主存中一个组内的块数与Cache中的分组数相同,组间采用直接映射,组内采用全相联映射。

替换算法:

随机替换算法:在发生替换时,该算法随机挑选一个候选的Cache行来进行替换,而与使用情况无关。

先进先出算法:把最先导入的哪一个Cache行替换出去

最近最少使用算法:统计哪一个Cache行是近段时间内使用次数最少的Cache行,需要替换时就将它替换出去

拓展

- 字拓展:作为整体顺序编址

- 位拓展:地址相同的存储器拼接起来

- 字位拓展:按照字扩展的方式增加存储器字的数量,同时按照位扩展的方法增加存储字长

主存储器与CPU的连接 P228 179-183(综合题)

第六章 指令系统(简答题)

P245 CISC的特点

指令系统复杂,具体表现为指令条数多、寻址方式多、指令格式多。CPU采用微程序控制实现指令的绘制执行,有较多的寄存器。由于指令丰富,程序员编程时有较大的选择空间,缩短了汇编指令条数。

P246 RISC的特点

指令系统设计时选择一些使用频度较高的简单指令,指令长度固定且操作码位置固定,指令格式种类少,寻址方式减少且简化。CPU中通用寄存器的数量相当多,可以减少访存次数。可以充分利用VLSI芯片的面积,给设计单芯片处理器带来很多好处,有利于提高性能。

第七章

控制器的组成

程序计数器、指令寄存器、指令译码器、操作控制信号形成部件、时序信号产生器、地址寄存器、数据寄存器

单周期的硬布线控制器设计(综合题、实验十)

If you like this blog or find it useful for you, you are welcome to comment on it. You are also welcome to share this blog, so that more people can participate in it. If the images used in the blog infringe your copyright, please contact the author to delete them. Thank you !